- Sector Numbering Convention:

- Download and print the sector test sheet Here (Pdf)

- Bias current comparison untill 18/07/2006 I_sector_ladders(xls)

- Issues Summary SectorTestsSumary.xls(xls)

- Sector Functionality Test Sheet Sector_Functionality_Tests.doc(doc)

HalfStaveTables

| sector 0 | sector 1 | sector 2 | sector 5 | |||||

|---|---|---|---|---|---|---|---|---|

| HS | Side A | Side C | Side A | Side C | Side A | Side C | Side A | Side C |

| 0 | 25_R | 26_L | 38_R | 37_L | 50_R | 55_L | 99_R | 100_L |

| 1 | 24_R | 23_L | 36_R | 39_L | 44_R | 51_L | 97_R | 98_L |

| 2 | 22_L | 19_R | 35_L | 30_R | 43_L | 45_R | 85_L | 95_R |

| 3 | 18_L | 9_R | 34_L | 27_R | 46_L | 48_R | 94_L | 93_R |

| 4 | 15_L | 16_R | 28_L | 32_R | 49_L | 47_R | 89_L | 90_R |

| 5 | 13_L | 10_R | 31_L | 33_R | 42_L | 40_R | 87_L | 88_R |

Half Barrel Tests

Sector Numbering conversion

1st half-barrel

- Sector 0 -> Sector 6 in DSF sector test

- Sector 1 -> Sector 3 in DSF sector test

- Sector 2 -> Sector 4 in DSF sector test

- Sector 3 -> Sector 2 in DSF sector test

- Sector 4 -> Sector 5 in DSF sector test

Sector 8

Sector 8 I-V curves

Side A

| HS0 | HS1 | HS2 | HS3 | HS4 | HS5 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| V(v) | I(wA) | V(v) | I(wA) | V(v) | I(wA) | V(v) | I(wA) | V(v) | I(wA) | V(v) | I(wA) |

| 2.6 | 1.03 | 2.25 | 0.5 | 2.05 | 0.75 | 2.15 | 0.69 | 2.35 | 1.16 | 2.15 | 1.29 |

| 10.45 | 1.16 | 10.10 | 0.79 | 10.05 | 1.07 | 10.10 | 0.99 | 10.3 | 0.72 | 10.10 | 6.55 |

| 15.30 | 1.16 | 15.00 | 0.66 | 15.05 | 0.97 | 15.05 | 0.99 | 15.35 | 0.68 | - | - |

| 20.15 | 1.17 | 19,9 | 0.52 | 20.10 | 0.94 | 20.05 | 1.02 | 20.35 | 0.66 | - | - |

| 25.15 | 1.18 | 24.80 | 0.46 | 25.10 | 0.94 | 25.00 | 1.09 | 25.3 | 0.65 | - | - |

| 30.05 | 1.19 | 29.70 | 0.43 | 30.20 | 0.98 | 30.00 | 1.16 | 30.25 | 0.65 | - | - |

| 34.95 | 1.21 | 34.55 | 0.43 | 35.20 | 1.08 | 35.00 | 1.56 | 35.3 | 0.66 | - | - |

| 39.95 | 1.25 | 39.50 | 0.40 | 40.25 | 1.20 | 39.95 | 1.42 | 40.3 | 0.68 | - | - |

| 44.75 | 1.77 | 44.35 | 0.42 | 45.20 | 1.37 | 44.90 | 1.43 | 45.25 | 0.70 | - | - |

| 49.75 | 1.91 | 49.25 | 0.48 | 50.30 | 1.58 | 49.9 | 1.44 | 50.25 | 0.72 | - | - |

Side C

| HS0 | HS1 | HS2 | HS3 | HS4 | HS5 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| V(v) | I(wA) | V(v) | I(wA) | V(v) | I(wA) | V(v) | I(wA) | V(v) | I(wA) | V(v) | I(wA) |

| 1.80 | 0.97 | 2.00 | 0.20 | 2.00 | 0.92 | 2.50 | 0.46 | 2.15 | 0.79 | 1.85 | 0.84 |

| 4.80 | 0.93 | 5.00 | 1.49 | 4.90 | 0.95 | 5.45 | 0.42 | 5.05 | 0.99 | 4.85 | 1.09 |

| 9.85 | 0.92 | 10.00 | 0.97 | 10.05 | 0.63 | 10.40 | 0.41 | 10.05 | 0.80 | 9.85 | 1.11 |

| 14.85 | 0.89 | 15.00 | 0.56 | 15.05 | 0.58 | 15.3 | 0.42 | 15.00 | 0.68 | 14.90 | 1.14 |

| 19.90 | 0.90 | 19.95 | 0.41 | 20.05 | 0.59 | 20.20 | 0.44 | 19.90 | 0.63 | 19.90 | 1.17 |

| 24.95 | 0.91 | 24.95 | 0.35 | 25.00 | 0.62 | 25.10 | 0.45 | 24.90 | 0.61 | 24.90 | 1.19 |

| 30.00 | 0.93 | 29.95 | 0.32 | 30.05 | 0.64 | 30.05 | 0.46 | 29.85 | 0.65 | 29.95 | 1.22 |

| 35.00 | 0.95 | 34.95 | 0.40 | 34.95 | 0.76 | 34.95 | 0.48 | 34.85 | 0.83 | 34.95 | 1.27 |

| 40.05 | 0.99 | 39.95 | 0.70 | 40.10 | 1.00 | 39.90 | 0.50 | 39.80 | 1.25 | 39.95 | 1.40 |

| 45.10 | 1.09 | 44.95 | 1.25 | 45.05 | 1.29 | 44.85 | 0.56 | 44.65 | 1.89 | 44.95 | 1.71 |

| 50.10 | 1.25 | 49.95 | 2.06 | 50.05 | 1.59 | 49.75 | 0.68 | 49.65 | 2.82 | 49.95 | 2.30 |

Sector 7

Side A

| CH0 | CH1 | CH2 | CH3 | CH4 | CH5 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| U(V) | I(uA) | U(V) | I(uA) | U(V) | I(uA) | U(V) | I(uA) | U(V) | I(uA) | U(V) | I(uA) |

| 2 | 0.71 | 2 | 0.98 | 2 | 1.33 | 2 | 0.84 | 2 | 0.58 | 2 | 0.70 |

| 5 | 0.91 | 5 | 1.57 | 5 | 1.54 | 5 | 1.15 | 5 | 1.25 | 5 | 1.18 |

| 10 | 0.85 | 10 | 1.42 | 10 | 1.24 | 10 | 0.92 | 10 | 0.92 | 10 | 1.09 |

| 15 | 0.83 | 15 | 1.35 | 15 | 1.06 | 15 | 0.82 | 15 | 0.80 | 15 | 1.04 |

| 20 | 0.83 | 20 | 1.36 | 20 | 1.01 | 20 | 0.82 | 20 | 0.75 | 20 | 1.00 |

| 30 | 0.82 | 30 | 1.40 | 30 | 0.98 | 30 | 1.13 | 30 | 0.70 | 30 | 0.96 |

| 40 | 0.83 | 40 | 1.50 | 40 | 1.03 | 40 | 1.91 | 40 | 0.72 | 40 | 1.07 |

| 50 | 0.90 | 50 | 2.12 | 50 | 1.24 | 50 | 2.97 | 50 | 0.79 | 50 | 2.11 |

Side C

| CH0 | CH1 | CH2 | CH3 | CH4 | CH5 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| U(V) | I(uA) | U(V) | I(uA) | U(V) | I(uA) | U(V) | I(uA) | U(V) | I(uA) | U(V) | I(uA) |

| 2 | 0.71 | 2 | 0.51 | 2 | 1.36 | 2 | 0.60 | 2 | 0.69 | 2 | 0.68 |

| 5 | 0.92 | 5 | 0.60 | 5 | 1.84 | 5 | 1.58 | 5 | 1.16 | 5 | 1.19 |

| 10 | 0.86 | 10 | 0.49 | 10 | 1.42 | 10 | 1.04 | 10 | 0.97 | 10 | 1.04 |

| 15 | 0.84 | 15 | 0.43 | 15 | 1.15 | 15 | 0.87 | 15 | 0.86 | 15 | 0.95 |

| 20 | 0.84 | 20 | 0.40 | 20 | 1.03 | 20 | 0.81 | 20 | 0.81 | 20 | 0.90 |

| 30 | 0.84 | 30 | 0.36 | 30 | 0.94 | 30 | 0.78 | 30 | 0.83 | 30 | 0.87 |

| 40 | 0.85 | 40 | 0.35 | 40 | 0.93 | 40 | 0.85 | 40 | 1.02 | 40 | 0.86 |

| 50 | 0.88 | 50 | 0.36 | 50 | 1.00 | 50 | 1.06 | 50 | 1.45 | 50 | 0.90 |

Sector 5

Side A

| HS | HS ID | Ladder 1 | Ladder 2 | PIXEL_BUS | MCM | Coment |

|---|---|---|---|---|---|---|

| HS0 | 99_R | Bias Current high | ||||

| HS1 | 97_R | ok | ||||

| HS2 | 85_L | One inefficient column (15) on chip 6. | ||||

| HS3 | 94_L | Bias with high current (9uA@35V) | ||||

| HS4 | 89_L | ok | ||||

| HS5 | 87_L | ok | ||||

Side C

| HS | HS ID | Ladder 1 | Ladder 2 | PIXEL_BUS | MCM | Coment |

|---|---|---|---|---|---|---|

| HS0 | 100_L | Slightly light sensitive ( current changed 1 micro amp) bias current too high, settings changed the bias current looked good first time we connected | ||||

| HS1 | 98_L | ok | ||||

| HS2 | 95_R | bias voltage set at 40 v | ||||

| HS3 | 93_R | ok | ||||

| HS4 | 90_R | ok | ||||

| HS5 | 88_R | "Uniformity Matrix looks strange with some of the last rows ending up around first rows.Problem with fiber optic cables, cannot configure.Changing the Fiber looks like it cured the problem.HS has pixel0 noisier than the rest, PVTH set to 190" | ||||

Sector 4

Side A

| HS | HS ID | Ladder 1 | Ladder 2 | PIXEL_BUS | MCM | Coment |

|---|---|---|---|---|---|---|

| HS0 | Lcern_VTT_277 | Lcern_VTT_278 | R28 (LOT P77-3) | RP25 | ok | |

| HS1 | Lct_VTT_251 | Lct_VTT_253 | R38(Lot6-P83-1) | RP21 | Hot HS | |

| HS2 | Lct_VTT_235 | Lct_VTT_162 | L35 (Lot6 P82-5) | LP27 | ok | |

| HS3 | Lct_VTT_233 | Lct_VTT_234 | LP28 | ok | ||

| HS4 | Lct_VTT_199 | Lct_VTT_200 | L11 | LP11 | ok | |

| HS5 | Lct_VTT_197 | Lct_VTT_198 | L28 (Lot5 P80-4) | LP16 | ok | |

Side C

| HS | HS ID | Ladder 1 | Ladder 2 | PIXEL_BUS | MCM | Coment |

|---|---|---|---|---|---|---|

| HS0 | Lct_VTT_254 | Lct_VTT_255 | L33 (LOT6-P82-3) | LP13 | ok | |

| HS1 | Lct_VTT_245 | Lct_VTT_236 | L31(Lot6-P82-1) | L08 | ok | |

| HS2 | Lcern_VTT_52 | Lcern_VTT_176 | R39 (Lot6 P32-2) | RP24 | ok | |

| HS3 | Lct_VTT_243 | Lct_VTT_248 | R40 (Lot6 P83-3) | R09 | ok | |

| HS4 | Lcern_VTT_261 | Lcern_VTT_263 | R33 (Lot5 P79-2) | RP26 | ok | |

| HS5 | Lct_VTT_230 | Lct_VTT_231 | R32 | RP16 | ok | |

Sector 3

Side A

| HS | HS ID | Ladder 1 | Ladder 2 | PIXEL_BUS | MCM | Coment |

|---|---|---|---|---|---|---|

| HS0 | 70_R | ok | ||||

| HS1 | 68_R | Hot HS | ||||

| HS2 | 65_L | Bias needs training, (44.8- 7.01) degradation (41.8- 8.1) | ||||

| HS3 | 62_L | ok | ||||

| HS4 | 61_L | ok | ||||

| HS5 | 56_L | ok | ||||

Side C

| HS | HS ID | Ladder 1 | Ladder 2 | PIXEL_BUS | MCM | Coment |

|---|---|---|---|---|---|---|

| HS0 | 69_L | ok | ||||

| HS1 | 67_L | ok | ||||

| HS2 | 64_R | Bias needs training (35 - 7.76) degradation second time on (31.9- 8.15) | ||||

| HS3 | 63_R | ok | ||||

| HS4 | 60_R | High temperature in the MCM (30 degrees) | ||||

| HS5 | 57_R | Bias needs Training, trips at 50V after some time (34v-8.6), light sensitive | ||||

Sector 2

Side A

| HS | HS ID | Ladder 1 | Ladder 2 | PIXEL_BUS | MCM | Comment |

|---|---|---|---|---|---|---|

| HS0 | 50_R | VTT85 | VTT189 | Bias needs training | ||

| HS1 | 44_R | VTT106 | VTT107 | |||

| HS2 | 43_L | VTT108 | VTT110 | |||

| HS3 | 46_L | VTT138 | VTT139 | |||

| HS4 | 49_L | VTT141 | VTT161 | Bias cannot go higher than 2 V | ||

| HS5 | 42_L | VTT165 | VTT169 | Short in extender solved | ||

12/07/2006

Test with black cover

| Without Configuration | ||||||

|---|---|---|---|---|---|---|

| HS | I MCM(A) | I Bus(A) | I Bias@50V(uA) | Temp(C) | Delay(s) | Misc Control |

| 0 | 0.42 | 6.00 | 9.10 | 37.5 | - | - |

| 1 | 0.42 | 5.33 | 0.35 | 32.3 | - | - |

| 2 | 0.42 | 5.62 | 1.36 | 33.8 | - | - |

| 3 | 0.39 | 5.28 | 1.37 | 31.2 | - | - |

| 4 | 0.41 | 5.54 | 7.40* | 30.9 | - | - |

| 5** | - | - | - | - | - | - |

* Bias @ 7V ** HS5 Short on extender (bus)

| With Configuration | ||||||

|---|---|---|---|---|---|---|

| HS | I MCM(A) | I Bus(A) | I Bias@50V(uA) | Temp(C) | Delay(s) | Misc Control |

| 0 | 0.42 | 5.62 | 4.19* | 37.1 | - | - |

| 1 | 0.41 | 5.58 | 0.35 | 32.8 | 33 | 128 |

| 2 | 0.41 | 5.59 | 1.30 | 33.9 | 33 | 128 |

| 3 | 0.39 | 5.35 | 1.24 | 31.4 | 33 | 128 |

| 4 | 0.41 | 5.81 | 1.21* | 31.4 | - | - |

| 5** | - | - | - | - | - | - |

* HS0 VBias = 30V, HS4 VBias = 2V ** HS5 Short on extender (bus)

| Min Treshold | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| HS | pixelChip 0 | pixelChip 1 | pixelChip 2 | pixelChip 3 | pixelChip 4 | pixelChip 5 | pixelChip 6 | pixelChip 7 | pixelChip 8 | pixelChip 9 |

| 0 | 220 | 210 | 210 | 210 | 210 | 205 | 205 | 200 | 205 | 205 |

| 1 | 215 | 210 | 210 | 205 | 210 | 210 | 205 | 210 | 210 | 205 |

| 2 | 210 | 215 | 210 | 210 | 205 | 200 | 210 | 210 | 205 | 210 |

| 3 | 215 | 215 | 215 | 215 | 220 | 210 | 215 | 215 | 220 | 215 |

| 4 | 205 | 205 | 210 | 215 | 205 | 205 | 205 | 205 | 205 | 205 |

| 5** | - | - | - | - | - | - | - | - | - | - |

** HS5 Short on extender (bus)

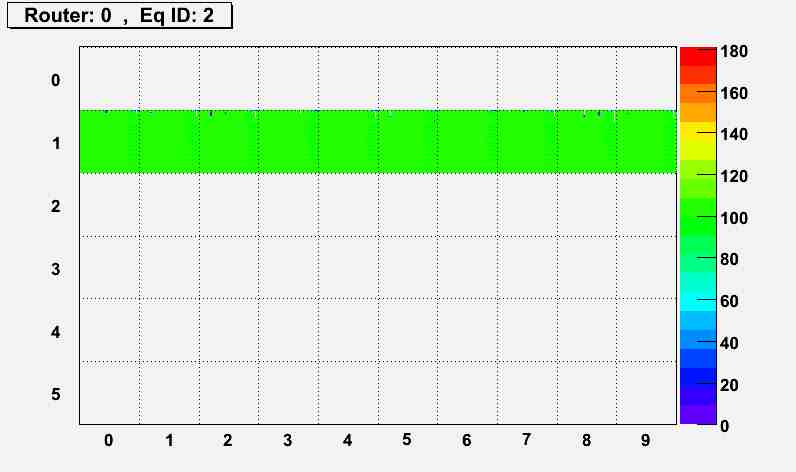

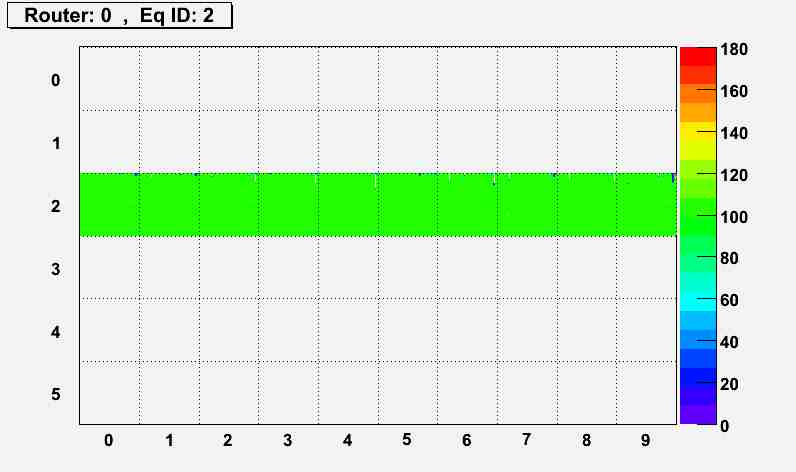

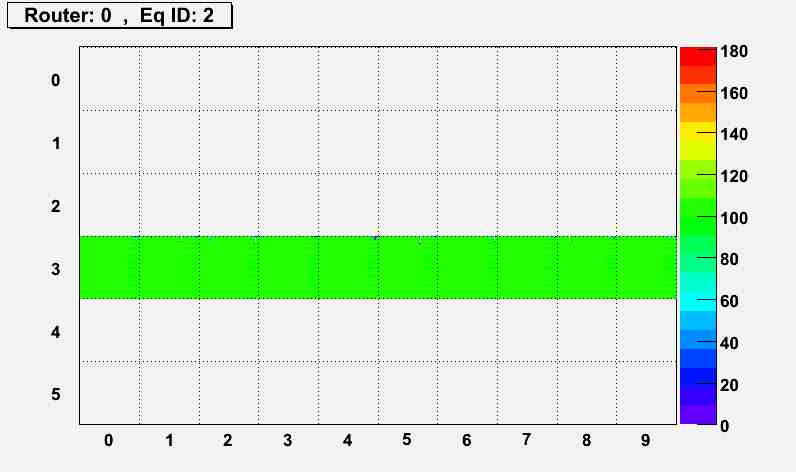

Uniformity Scan Screenshots

HS1 Pre_VTH@200 full view

HS2 Pre_VTH@200 full view

HS3 Pre_VTH@200 full view

18/07/2006

Test without black cover

| Without Configuration | ||||||

|---|---|---|---|---|---|---|

| HS | I MCM(A) | I Bus(A) | I Bias@50V(uA) | Temp(C) | Delay(s) | Misc Control |

| 0 | 0.42 | 5.60 | 5.73* | 37.4 | - | - |

| 1 | 0.41 | 5.58 | 0.53 | 32.1 | - | - |

| 2 | 0.41 | 5.58 | 1.67 | 33.6 | - | - |

| 3 | 0.39 | 5.34 | 2.04 | 30.8 | - | - |

| 4 | 0.41 | 5.53 | 1.53* | 30.6 | - | - |

| 5** | - | - | - | - | - | - |

* HS0 VBias = 30V, HS4 VBias = 2V ** HS5 Short on extender (bus)

| With Configuration | ||||||

|---|---|---|---|---|---|---|

| HS | I MCM(A) | I Bus(A) | I Bias@50V(uA) | Temp(C) | Delay(s) | Misc Control |

| 0 | 0.42 | 5.59 | 5.84* | 36.9 | - | - |

| 1 | 0.41 | 5.58 | 0.53 | 32.6 | - | - |

| 2 | 0.41 | 5.58 | 1.66 | 33.8 | - | - |

| 3 | 0.39 | 5.34 | 2.08 | 31.2 | - | - |

| 4 | 0.41 | 5.81 | 1.50* | 31.2 | - | - |

| 5** | - | - | - | - | - | - |

* HS0 VBias = 30V, HS4 VBias = 2V ** HS5 Short on extender (bus)

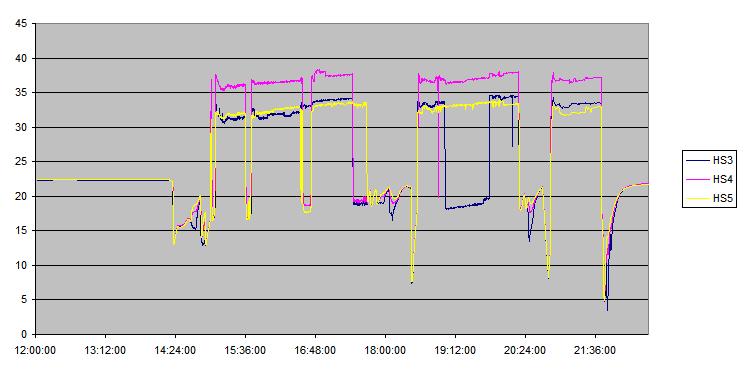

Temperature Screenshots

- HS1 With Configuration @50V , HS1 Without Configuration

- HS2 With Configuration @50V , HS2 Without Configuration

- HS3 With Configuration @50V , HS3 Without Configuration

- HS4 With Configuration , HS4 Without Configuration

- Inner Layer With Configuration @50V , Inner Layer Without Configuration , Inner Layer Without Power

- Outer Layer With Configuration @50V , Outer Layer Without Configuration , Outer Layer Without Power

Sector 2 Side C

| HS | HS ID | Ladder 1 | Ladder 2 | PIXEL_BUS | MCM | Comment |

|---|---|---|---|---|---|---|

| HS0 | 55_L | VTT194 | VTT202 | ok | ||

| HS1 | 51_L | VTT84 | VTT153 | Only half of chip 8 responds | ||

| HS2 | 45_R | VTT90 | VTT92 | ok | ||

| HS3 | 48_R | VTT129 | VTT137 | Light sensitive, ValBuffout DAC had to change configuration to 192 | ||

| HS4 | 47_R | VTT134 | VTT135 | ok | ||

| HS5 | 40_R | VTT152 | VTT173 | Bias needs training | ||

03/07/2006

Temperature Screenshots

| Working Data | ||||||

|---|---|---|---|---|---|---|

| HS | I MCM(A) | I Bus(A) | I Bias@50V(uA) | Temp(C) | Delay(s) | Misc Control |

| 0 | 0.40 | 5.57 | 1.010 | - | 33 | 128 |

| 1 | 0.41 | 5.65 | 3.450 | - | - | - |

| 2 | 0.42 | 5.08 | 1.610 | - | - | - |

| 3 | 0.40 | 5.45 | 0.490* | - | - | - |

| 4 | 0.38 | 5.16 | 1.080 | - | - | - |

| 5 | 0.40 | 4.94 | 1.810* | - | - | - |

* Light Sensitive Bias @ 20V

| Min Treshold | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| HS | pixelChip 0 | pixelChip 1 | pixelChip 2 | pixelChip 3 | pixelChip 4 | pixelChip 5 | pixelChip 6 | pixelChip 7 | pixelChip 8 | pixelChip 9 |

| 0 | 215 | 215 | 215 | 205 | 215 | 225 | 220 | 225 | 195 | 220 |

| 1 | - | - | - | - | - | - | - | - | - | - |

| 2 | - | - | - | - | - | - | - | - | - | - |

| 3 | - | - | - | - | - | - | - | - | - | - |

| 4 | - | - | - | - | - | - | - | - | - | - |

| 5 | - | - | - | - | - | - | - | - | - | - |

Temperature Screenshots

- HS0 With Configuration @2V , HS0 With Configuration @50V , HS0 Without Configuration

- HS1 With Configuration @2V , HS1 With Configuration @50V , HS1 Without Configuration

- HS2 With Configuration @2V , HS2 With Configuration @50V , HS2 Without Configuration

- HS3 With Configuration @2V , HS3 With Configuration @20V , HS3 Without Configuration

- HS4 With Configuration @2V , HS4 With Configuration @50V , HS4 Without Configuration

- HS5 With Configuration @2V , HS5 With Configuration @20V , HS5 Without Configuration

- Inner Layer With Configuration @2V , Inner Layer With Configuration @50V , Inner Layer Without Configuration , Inner Layer Without Power

- Outer Layer With Configuration @2V , Outer Layer With Configuration @50V , Outer Layer Without Configuration , Outer Layer Without Power

07/07/2006

Test with black cover

| Working Data | ||||||

|---|---|---|---|---|---|---|

| HS | I MCM(A) | I Bus(A) | I Bias@50V(uA) | Temp(C) | Delay(s) | Misc Control |

| 0 | 0.41 | 5.57 | 0.13 | 31.85 | - | - |

| 1 | 0.40 | 5.66 | 3.12 | 32.69 | 33 | 128 |

| 2 | 0.42 | 5.08 | 1.19 | 31.61 | 33 | 128 |

| 3 | 0.40 | 5.46 | 6.28* | 30.11 | 34 | 192 |

| 4 | 0.38 | 5.15 | 0.70 | 29.13 | 33 | 128 |

| 5 | 0.40 | 4.93 | 1.67* | 29.98 | 33 | 128 |

* HS3 @ 37V, HS5 @ 20V

| Min Treshold | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| HS | pixelChip 0 | pixelChip 1 | pixelChip 2 | pixelChip 3 | pixelChip 4 | pixelChip 5 | pixelChip 6 | pixelChip 7 | pixelChip 8 | pixelChip 9 |

| 0 | - | - | - | - | - | - | - | - | - | - |

| 1 | 205 | 220 | 205 | 200 | 205 | 210 | 220 | 220 | 215 | 220 |

| 2 | 220 | 215 | 215 | 205 | 200 | 205 | 210 | 210 | 220 | 210 |

| 3 | 215 | 215 | 215 | 210 | 210 | 215 | 220 | 215 | 210 | 215 |

| 4 | 210 | 205 | 205 | 210 | 210 | 210 | 210 | 210 | 210 | 210 |

| 5 | 210 | 205 | 205 | 215 | 215 | 205 | 210 | 210 | 215 | 215 |

10/07/2006

Test without black cover, in wich "pre_VIPREAM" DAC changes to uniform the temperature on HS0, 4, 5

pre_VIPREAM=128.

| Working Data | ||||||

|---|---|---|---|---|---|---|

| HS | I MCM(A) | I Bus(A) | I Bias@50V(uA) | Temp(C) | Delay(s) | Misc Control |

| 0 | 0.40 | 5.57 | 1.01 | 31.04 | - | - |

| 4 | 0.38 | 5.17 | 1.74 | 29.0 | - | - |

| 5 | 0.40 | 4.95 | 4.30* | 29.8 | - | - |

* HS5 @ 26V.

chip 0-4 @ pre_VIPREAM=170, chip 5-9 @ pre_VIPREAM=128.

| Min Treshold | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| HS | pixelChip 0 | pixelChip 1 | pixelChip 2 | pixelChip 3 | pixelChip 4 | pixelChip 5 | pixelChip 6 | pixelChip 7 | pixelChip 8 | pixelChip 9 |

| 0 | 215 | 215 | 215 | 205 | 215 | 225 | 225 | 225 | 225 | 220 |

chip 0-4 @ pre_VIPREAM=190, chip 5-9 @ pre_VIPREAM=128.

| Working Data | ||||||

|---|---|---|---|---|---|---|

| HS | I MCM(A) | I Bus(A) | I Bias@50V(uA) | Temp(C) | Delay(s) | Misc Control |

| 0 | 0.40 | 5.07 | 0.99 | 31.04 | - | - |

| 4 | 0.38 | 4.69 | 1.64 | 28.4 | - | - |

| 5 | 0.41 | 4.52 | 4.00* | 29.0 | - | - |

* HS5 @ 26V.

| Min Treshold | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| HS | pixelChip 0 | pixelChip 1 | pixelChip 2 | pixelChip 3 | pixelChip 4 | pixelChip 5 | pixelChip 6 | pixelChip 7 | pixelChip 8 | pixelChip 9 |

| 0 | 215 | 215 | 215 | 205 | 215 | 225 | 225 | 225 | 225 | 220 |

| 4 | 205 | 205 | 205 | 205 | 205 | 210 | 215 | 215 | 210 | 210 |

| 5 | 210 | 205 | 205 | 215 | 215 | 210 | 210 | 210 | 215 | 195 |

11/07/2006

Test with black cover

Test to investigate the Half chip response of chip8 on HS1

| Test Value | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Run Number | pre_VTH | Valbuffout | GTL ref(mV) | Stb lengh | ||||||

| 652 | 220 | 200 | 862 | 1 | ||||||

| 653 | 215 | 200 | 862 | 1 | ||||||

| 654 | 225 | 200 | 862 | 1 | ||||||

| 655 | 230 | 190 | 862 | 1 | ||||||

| 656 | 230 | 150 | 862 | 1 | ||||||

| 657 | 230 | 128 | 862 | 1 | ||||||

| 658 | 230 | 128 | 711* | 1 | ||||||

| 659 | 230 | 128 | 900** | 1 | ||||||

| 661 | 230 | 220 | 862 | 4 | ||||||

| 662 | 230 | 220 | 862 | 6 | ||||||

| 663 | 230 | 220 | 862 | 8 | ||||||

| 664 | 230 | 220 | 862 | 10 | ||||||

| 665 | 230 | 220 | 862 | 12 | ||||||

| 666 | 230 | 220 | 862 | 15 | ||||||

| 667 | 230 | 250 | 862 | 1 | ||||||

*IBus = 5.50 A. **IBus = 5.51 A.

I V Courve for HS 3 and 5 (trainig)

| HS3 | |

|---|---|

| VBias (V) | IBias (uA) |

| 2 | 0.03 |

| 37 | 6.29 |

| 40 | 7.68 |

| HS5 | |

|---|---|

| VBias (V) | IBias (uA) |

| 2 | 0.47 |

| 35 | 6.50 |

| 40 | 8.32 |

Test to investigate Double pixel pulsing of chip 8 on HS3

| Test Value | ||||

|---|---|---|---|---|

| Run Number | pre_VTH | Valbuffout | Line set | Line Read |

| 668 | 200 | 220 | 128 _ 192 | 128;129 _ 192;193 |

| 670 | 200 | 200 | 128 _ 192 | 128;129 _ 192;193 |

| 671 | 200 | 192 | 128 _ 192 | 128 _ 192 |

---+++Sector 1 Side C

Summary Table 1C

| HS | HS ID | Ladder 1 | Ladder 2 | PIXEL_BUS | MCM | Comment |

|---|---|---|---|---|---|---|

| HS0 | 37_L | VTT157 | VTT158 | ok | ||

| HS1 | 39_L | VTT95 | VTT150 | ok | ||

| HS2 | 30_R | VTT116 | VTT115 | ok | ||

| HS3 | 27_R | VTT69 | VTT82 | ok | ||

| HS4 | 32_R | VTT142 | VTT145 | ok | ||

| HS5 | 33_R | VTT98 | VTT114 | ok | ||

12/06/2006

| Working Data | ||||||

|---|---|---|---|---|---|---|

| HS | I MCM(A) | I Bus(A) | I Bias(uA) | Temp(C) | Delay(s) | Misc Control |

| 0 | 0.39 | 5.26 | 2.35 | 31.69 | 33 | 128 |

| 1 | 0.31 | 5.13 | 7.58 | 30.88 | 33 | 128 |

| 2 | 0.32 | 5.30 | 0.96 | 29.53 | 33 | 128 |

| 3 | 0.38 | 4.70 | 6.71 | 29.68 | 33 | 128 |

| 4 | 0.31 | 5.16 | 1.70 | 31.43 | 33 | 128 |

| 5 | 0.33 | 5.31 | 2.37 | 30.25 | 33 | 128 |

| Min Treshold | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| HS | pixelChip 0 | pixelChip 1 | pixelChip 2 | pixelChip 3 | pixelChip 4 | pixelChip 5 | pixelChip 6 | pixelChip 7 | pixelChip 8 | pixelChip 9 |

| 0 | 210 | 210 | 215 | 210 | 205 | 210 | 210 | 215 | 205 | 210 |

| 1 | 225 | 220 | 225 | 220 | 220 | 225 | 225 | 225 | 225 | 225 |

| 2 | 205 | 210 | 210 | 210 | 210 | 210 | 210 | 210 | 210 | 210 |

| 3 | 215 | 220 | 215 | 215 | 210 | 210 | 210 | 215 | 215 | 215 |

| 4 | 210 | 210 | 215 | 215 | 210 | 210 | 215 | 215 | 215 | 210 |

| 5 | 215 | 215 | 215 | 215 | 215 | 215 | 215 | 215 | 215 | 220 |

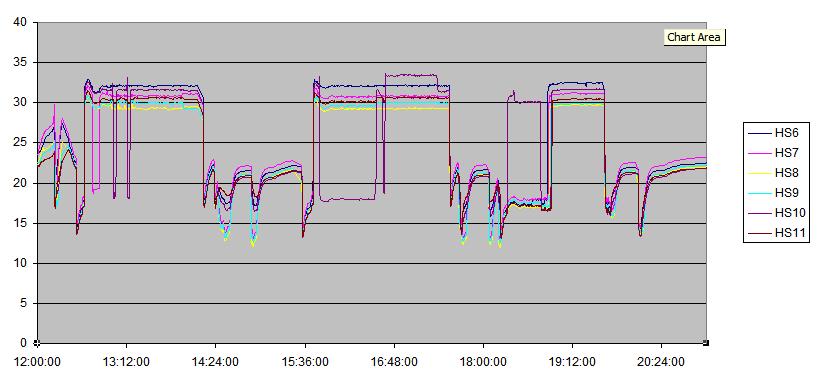

Temp Plot Sect1 Side C 12/06/2006

Sector 1

Side A

| HS | HS ID | Ladder 1 | Ladder 2 | PIXEL_BUS | MCM | Comment |

|---|---|---|---|---|---|---|

| HS0 | 38_R | VTT160 | VTT164 | Detached (changed needs retesting) | ||

| HS1 | 36_R | VTT93 | VTT130 | ok | ||

| HS2 | 35_L | VTT132 | VTT146 | Detached(changed needs retesting) | ||

| HS3 | 34_L | VTT70 | VTT124 | ok | ||

| HS4 | 28_L | VTT97 | VTT104 | ok | ||

| HS5 | 31_L | VTT126 | VTT128 | ok | ||

12/06/2006

| Working Data | ||||||

|---|---|---|---|---|---|---|

| HS | I MCM(A) | I Bus(A) | I Bias(uA) | Temp(C) | Delay(s) | Misc Control |

| 0 | 0.40 | 5.12 | 5.54 | 34.5 | 34 | 192 |

| 1 | 0.38 | 5.02 | 0.78 | 30.1 | 33 | 128 |

| 2 | - | - | - | - | - | - |

| 3 | 0.38 | 5.16 | 0.33 | 31.4 | 33 | 128 |

| 4 | 0.40 | 5.15 | 0.24 | 35.3 | 33 | 128 |

| 5 | 0.37 | 5.36 | 0.65 | 31.1 | 34 | 192 |

| Min Treshold | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| HS | pixelChip 0 | pixelChip 1 | pixelChip 2 | pixelChip 3 | pixelChip 4 | pixelChip 5 | pixelChip 6 | pixelChip 7 | pixelChip 8 | pixelChip 9 |

| 0 | 227 | 227 | 225 | 225 | 225* | 210 | 215 | 215 | 210 | 215 |

| 1 | 210 | 200 | 210 | 200 | 210 | 210 | 210 | 210 | 215 | 210 |

| 2 | - | - | - | - | - | - | - | - | - | - |

| 3 | 205 | 205 | 210 | 205 | 200 | 200 | 200 | 205 | 205 | 210 |

| 4 | 210 | 210 | 210 | 210 | 210 | 210 | 210 | 210 | 210 | 210 |

| 5 | 215 | 215 | 215 | 215 | 215 | 215 | 215 | 215 | 215 | 210 |

14/06/2006 Before Re-Work

| Working Data | ||||||

|---|---|---|---|---|---|---|

| HS | I MCM(A) | I Bus(A) | I Bias(uA) | Temp(C) | Delay(s) | Misc Control |

| 0 | - | - | - | - | - | - |

| 1 | - | - | - | - | - | - |

| 2 | - | - | - | - | - | - |

| 3 | 0.38 | 5.36 | 0.65 | 31.97 | 33 | 128 |

| 4 | 0.39 | 5.23 | 0.32 | 35.24 | 34 | 192 |

| 5 | 0.37 | 5.34 | 0.67 | 32.63 | 34 | 192 |

| Min Treshold | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| HS | pixelChip 0 | pixelChip 1 | pixelChip 2 | pixelChip 3 | pixelChip 4 | pixelChip 5 | pixelChip 6 | pixelChip 7 | pixelChip 8 | pixelChip 9 |

| 0 | - | - | - | - | - | - | - | - | - | - |

| 1 | - | - | - | - | - | - | - | - | - | - |

| 2 | - | - | - | - | - | - | - | - | - | - |

| 3 | 215 | 210 | 210 | 215 | 210 | 210 | 210 | 215 | 215 | 215 |

| 4 | 210 | 200 | 210 | 205 | 200 | 200 | 205 | 205 | 205 | 210 |

| 5 | 220 | 210 | 210 | 210 | 210 | 215 | 215 | 210 | 210 | 215 |

Temp Plot Side A 14/06/2006

15/06/2006 After Re-Work (With Clip)

| Working Data | ||||||

|---|---|---|---|---|---|---|

| HS | I MCM(A) | I Bus(A) | I Bias(uA) | Temp(C) | Delay(s) | Misc Control |

| 0 | - | - | - | - | - | - |

| 1 | - | - | - | - | - | - |

| 2 | - | - | - | - | - | - |

| 3 | 0.38 | 5.35 | 1.14 | 30.9 | 34 | 192 |

| 4 | 0.39 | 5.19 | 0.87 | 32.7 | 33 | 128 |

| 5 | 0.38 | 5.34 | 1.05 | 29.22 | 34 | 192 |

| Min Treshold | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| HS | pixelChip 0 | pixelChip 1 | pixelChip 2 | pixelChip 3 | pixelChip 4 | pixelChip 5 | pixelChip 6 | pixelChip 7 | pixelChip 8 | pixelChip 9 |

| 0 | - | - | - | - | - | - | - | - | - | - |

| 1 | - | - | - | - | - | - | - | - | - | - |

| 2 | - | - | - | - | - | - | - | - | - | - |

| 3 | 215 | 210 | 210 | 210 | 210 | 205 | 210 | 210 | 210 | 215 |

| 4 | 205 | 200 | 205 | 205 | 200 | 210 | 200 | 205 | 205 | 205 |

| 5 | 220 | 205 | 210 | 205 | 210 | 210 | 210 | 210 | 210 | 210 |

Temperature Plot Sector1 Side A 15/06/20006:

Sector 0

Side A

03/08/2006

| Channel | HS | Bus | Extender | Min T Bari | Min T CERN | I bus(A) | I bias @ 2v (uA) | Comment | |

|---|---|---|---|---|---|---|---|---|---|

| 0 | 25R | MR003 | S- | 182.1 | 205 | 4.49 | 1.36 | 27.8 | |

| 1 | 24R | MR001 | S- | 183.3 | - | 2.26 | 0.5 | 22.4 | Dead pixels in chip6, bias needs training (11uA@50V) |

| 2 | 22L | MR002 | S- | 190.5 | 217 | 5.09 | 1.01 | 28.48 | leakage current high (12.72uA@46.3V) |

| 3 | 18L | AL\CU020 | S- | 196 | - | 2.35 | 0.98 | 21.55 | leakage current increasing after some time (6.7uA@50V) |

| 4 | 15L | AL\CU012 | S- | 189.9 | 205 | 4.52 | 1.37 | 28.62 | Noisy in Uni-Matrix, Bias needs training |

| 5 | 13L | AL\CU018 | S- | 186 | 210 | 4.7 | 1.31 | 28.87 | Problem in uni-matrix for row 64 chip4 (testpulse in this row results in hits allover the chip), bias needs training (10.02uA@50V) |

Temperature Screenshots

- HS0 With Configuration @2V

- HS1 With Configuration @2V

- HS2 With Configuration @2V

- HS3 With Configuration @2V

- HS4 With Configuration @2V

- HS5 With Configuration @2V

Side C

03/08/2006

| Channel | HS | Bus | Extender | Min T Bari | Min T CERN | I bus(A) | I bias @ 2v (uA) | temp(Cº) | Comment |

|---|---|---|---|---|---|---|---|---|---|

| 0 | 26L | ML004 | S- | 185.9 | 205 | 4.27 | 0.89 | 29.35 | |

| 1 | 23L | ML005 | S- | 184.4 | - | - | - | - | Problem in Pt1000 chain reading, check cable |

| 2 | 19R | AL\CU013 | S- | 204 | 170 | 3.36 | 0.38 | 25.71 | chip 2 with a long test column chip 3 with strange uniformity (disappeared with strobe lengh to 2) |

| 3 | 9R | AL\CU004 | S- | 203 | 216 | 4.7 | 0.64 | 29.3 | Chip 8,9 with problems, already knowed, chip 3 with "scratch (eye lash?)" |

| 4 | 16R | AL\CU017 | S- | 203 | 215 | 4.12 | 1.22 | 30.1 | Uni-matrix 2dead column in chip3, light sensitive, bias needs training (11.53uA@25V) |

| 5 | 10R | AL\CU003 | S- | 204.8 | - | - | - | - | chip 0 with a noisy column |

Temperature Screenshots

- HS0 With Configuration @2V

- HS1 Without Power

- HS2 With Configuration @2V

- HS3 With Configuration @2V

- HS4 With Configuration @30V

- HS5 Without Power